- Quartus ii free download cnet for free#

- Quartus ii free download cnet drivers#

- Quartus ii free download cnet driver#

- Quartus ii free download cnet code#

Plug the USB-Blaster II cable into your PC.

Quartus ii free download cnet driver#

where 91 indicates the quartus version Driver Installation for Altera USB-Blaster II. c:\altera\91\quartus\drivers\usb-blaster.

Quartus ii free download cnet drivers#

Quartus ii free download cnet for free#

This tutorial uses FLEX10KE for simulation purpose.Download quartus ii web edition for free (Windows) Please note that this delay depends on the device chosen for the simulation. Figure 9 illustrates the timing parameter of our design file.

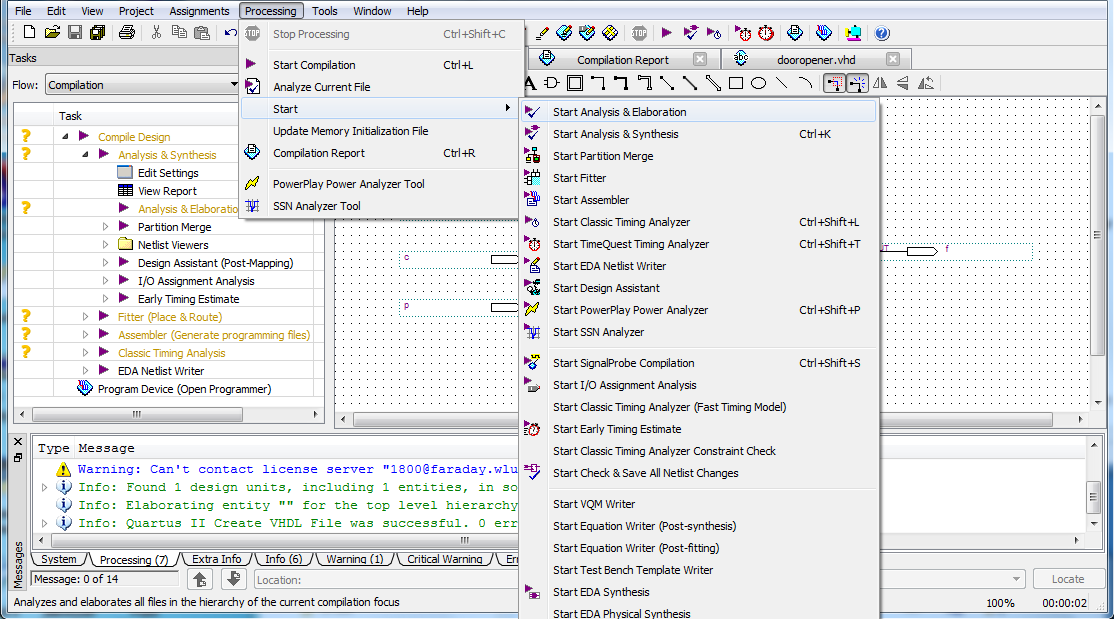

Timing Analyzer tool will provide propagation delays along all the paths and the worst case propagation delay. It is seen in Figure 8 that there are propagation delays between inputs and outputs. Figure 8 shows the simulation waveform from timing analysis. After successful compilation and simulation, simulation waveform will be diplayed. Timing simulation is carried out by selecting Processing > Start Compilation and Simulation. So, we have to change it back to Timing simulation mode to run timing simulation. We have changed the default setting to run the functional simulation. We will be able to find the propagation delay along various paths in the synthesized circuits. Timing simulation verifies both the logical correctness and timing. Having verified the logical correctness of the design file, it is necessary to determine whether the synthesized circuit meets the delay constraint. It is also seen that there is no time delay between input and output switching. Successful simulation will generate simulation waveform (Figure 7)Īs shown in the above figure, our design file correctly generates the output variables. We will select Process > Start Simulation to begin the simulation. Simulation will use a vector waveform file created earlier. Functional simulation netlist generationĪt this point, we are ready to run functional simulation.

Figure 6 shows the screen capture of the command and output.

Quartus ii free download cnet code#

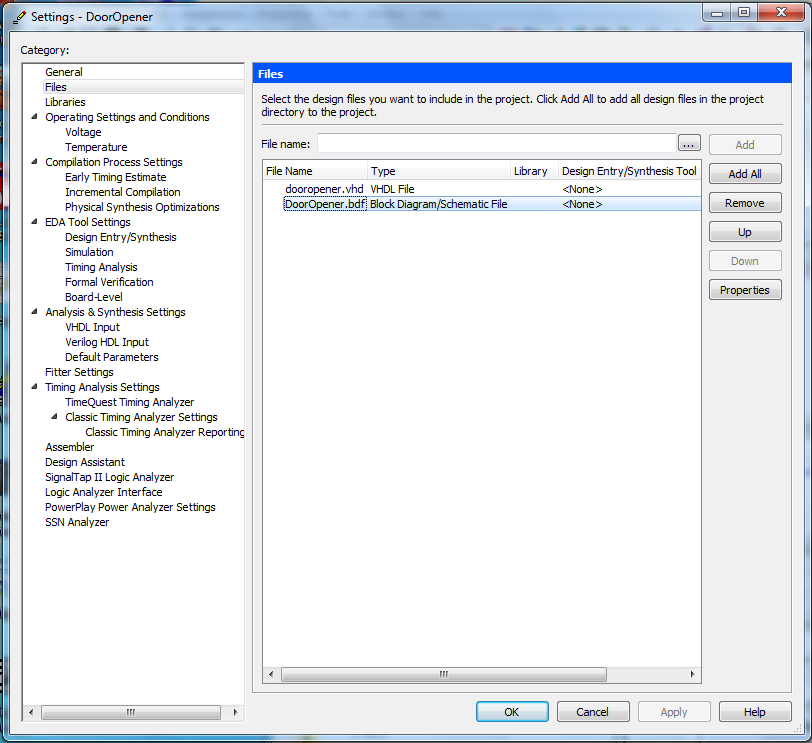

The circuit configuration and VHDL code for an 2-to-4 decoder are shown belowlibrary ieee - use the IEEE library use ieee.std_logic_1164.all - specify which package in the library to include entity Decoder_2_to_4 is port (A,B : in bit D0, D1, D2, D3 : out bit) end Decoder_2_to_4 architecture DECODER of Decoder_2_to_4 is begin D0 Generate functional Simulation Netlist. Please note that VHDL syntax and semantics are beyond the scope of this tutorial. Creating HDL Design Projects with Quartus IIIn this section, a new HDL project containing an 2-to-4 decoder will be designed and compiled with Quartus II. Please note that this tutorial is based on Altera Quartus II 8.1 web edition version. This tutorial will also introduce two types of simulation, namely, functional simulation and timing simulations, to assess the behavior and performance of the desired design. In this case, VHDL, Verilog or other HDL design files are used to synthesize and simulate the desired design. The second part of Quartus II tutorial is aimed at introducing HDL based design entry method. Hardware description languages (HDLs) provides standard text based expressions of the structure and behavior of digital circuits. It becomes very difficult to use this method for a large design with hundreds of primitive gates.

Altera Quartus II TutorialPart II(For ECE 465 Students at UIC)Sajjad Rahaman TA for ECE 465, Spring 2009 Department of Electrical and Computer Engineering University of Illinois at Chicago first part of Quartus II tutorial illustrates schematic diagram based entry for the desired circuit.

0 kommentar(er)

0 kommentar(er)